CPU Register - General Purpose Register (GPR)

About

The General purpose registers are available for storing:

Articles Related

Mode

CPU - Word size (8, 16, 32 and 64-bit)

32-bit

| Register | Name | Use |

|---|---|---|

| EAX | Accumulator | Accumulator for operands and results data, Used in arithmetic operations |

| EBX | Base | Pointer to data in the DS segment |

| ECX | Counter | Counter for string, loop and shift/rotate operations |

| EDX | Data | I/O pointer, used in arithmetic operations and I/O operations. |

| Stream Operations | ||

| ESI | Source Index | Pointer to data in the segment pointed to by the DS register; source pointer for string operations, Used as a pointer to a source in stream operations |

| EDI | Destination Index | Pointer to data (or destination) in the segment pointed to by the ES register; destination pointer for string operations, Used as a pointer to a destination in stream operations |

| Stack | ||

| ESP | Stack pointer | Stack pointer (in the SS segment), Pointer to the top of the stack. As a general rule it should not be used for another purpose. |

| EBP | Base Pointer | Base Pointer to data on the stack (in the SS segment), point to the base of the stack |

16-bit

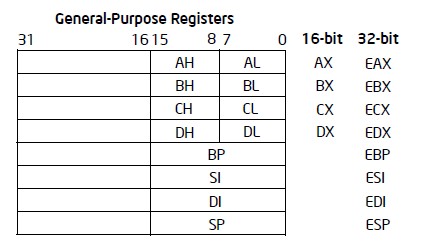

The following bit can be referenced by name:

- The lower 16 bits of the 32-bit general-purpose registers that map directly to the register set found in the 8086 and Intel 286 processors (.X)

- Each of the lower two bytes of the registers (.H for high and .L for low)

| 16-bit register | high bytes name | low bytes | 32-bit register |

|---|---|---|---|

| AX | AH | AL | EAX |

| BX | BH | BL | EBX |

| CX | CH | CL | ECX |

| DX | DH | DL | EDX |

| BP | EBP | ||

| SI | ESI | ||

| DI | EDI | ||

| SP | ESP |

64-bit

The Registers only available in 64-bit mode are R8-R15 and XMM8-XMM15.

Addressable General Purpose Registers:

| operand size | Register Type | Available Registers (With Rex) | Available Registers (Without REX) |

|---|---|---|---|

| 8-bit | Byte Registers | AL, BL, CL, DL, DIL, SIL, BPL, SPL, R8L - R15L | AL, BL, CL, DL, AH, BH, CH, DH |

| 16-bit | Word Registers | AX, BX, CX, DX, DI, SI, BP, SP, R8W - R15W | AX, BX, CX, DX, DI, SI, BP, SP |

| 32-bit | Doubleword Registers | EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP, R8D - R15D | EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP |

| 64-bit | Quadword Registers | RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, R8-R15 | NA |

REX prefixes are used to generate 64-bit operand sizes or to reference registers R8-R15.

Documentation / Reference

- Vol1 - 3.4 - Basic Program execution registers - https://software.intel.com/en-us/articles/intel-sdm

- The special uses of general-purpose registers by instructions are described in Chapter 5, “Instruction Set Summary,” in this volume. See also: Chapter 3, Chapter 4 and Chapter 5 of Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volumes 2A, 2B & 2C